# THE DATASHEET OF EVAL-ADXL357Z

## Low Noise, Low Drift, Low Power, 3-Axis MEMS Accelerometers

**Data Sheet**

ADXL356/ADXL357

#### **FEATURES**

Hermetic package offers optimal long-term stability 0 g offset vs. temperature (all axes): 0.75 mg/°C maximum Ultralow noise spectral density (all axes): 75  $\mu g/\sqrt{Hz}$

$\textbf{Low power, V}_{\text{SUPPLY}} \, \textbf{(LDO regulator enabled)}$

ADXL356 in measurement mode: 150  $\mu A$  ADXL357 in measurement mode: 200  $\mu A$

ADXL356/ADXL357 in standby mode: 21 μA

ADXL356 has user adjustable analog output bandwidth

**ADXL357 digital output features**

Digital SPI and limited I<sup>2</sup>C interfaces supported 20-bit ADC

Data interpolation routine for synchronous sampling

Programmable high- and low-pass digital filters

Integrated temperature sensor

**Voltage range options**

V<sub>SUPPLY</sub> with internal regulators: 2.25 V to 3.6 V

$V_{1P8ANA}, V_{1P8DIG}$  with internal LDO regulator bypassed: 1.8 V typical  $\pm$  10%

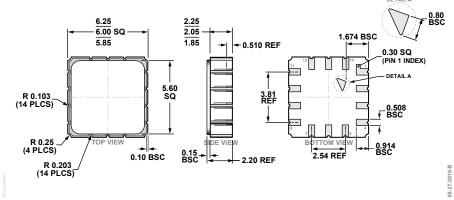

Operating temperature range:  $-40^{\circ}$ C to  $+125^{\circ}$ C 14-terminal, 6 mm  $\times$  5.6 mm  $\times$  2.2 mm, LCC package

#### **APPLICATIONS**

Inertial measurement units (IMUs)/attitude and heading reference systems (AHRSs)

Platform stabilization systems

Structural health monitoring

Seismic imaging

Tilt sensing

Robotics

Condition monitoring

#### **GENERAL DESCRIPTION**

The analog output ADXL356 and the digital output ADXL357 are low noise density, low 0 g offset drift, low power, 3-axis accelerometers with selectable measurement ranges. The ADXL356B supports the  $\pm 10~g$  and  $\pm 20~g$  ranges, the ADXL356C supports the  $\pm 10~g$  and  $\pm 40~g$  ranges, and the ADXL357 supports the  $\pm 10~g$ ,  $\pm 20~g$ , and  $\pm 40~g$  ranges.

The ADXL356/ADXL357 offer industry leading noise, minimal offset drift over temperature, and long-term stability, enabling precision applications with minimal calibration.

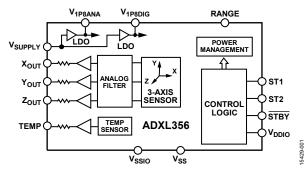

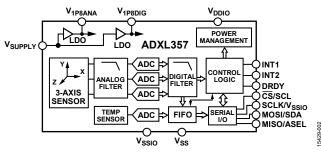

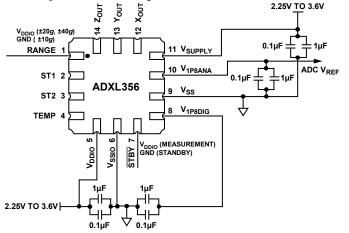

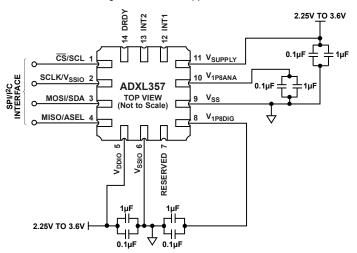

#### **FUNCTIONAL BLOCK DIAGRAMS**

Figure 1. ADXL356

Figure 2. ADXL357

The low drift, low noise, and low power ADXL357 enables accurate tilt measurement in an environment with high vibration. The low noise of the ADXL356 over higher frequencies is ideal for condition-based monitoring and other vibration sensing applications.

The ADXL357 multifunction pin names may be referenced only by their relevant function for either the serial peripheral interface (SPI) or limited I<sup>2</sup>C interface.

<sup>&</sup>lt;sup>1</sup> Protected by U.S. Patents 8,472,270; 9,041,462; 8,665,627; 8,917,099; 6,892,576; 9,297,825; and 7,956,621.

## **TABLE OF CONTENTS**

| Features 1                                                         |

|--------------------------------------------------------------------|

| Applications1                                                      |

| Functional Block Diagrams1                                         |

| General Description1                                               |

| Revision History3                                                  |

| Specifications4                                                    |

| Analog Output for the ADXL3564                                     |

| Digital Output for the ADXL3575                                    |

| SPI Digital Interface Characteristics for the ADXL357              |

| I <sup>2</sup> C Digital Interface Characteristics for the ADXL357 |

| Absolute Maximum Ratings9                                          |

| Thermal Resistance9                                                |

| Recommended Soldering Profile9                                     |

| ESD Caution9                                                       |

| Pin Configurations and Function Descriptions                       |

| Typical Performance Characteristics12                              |

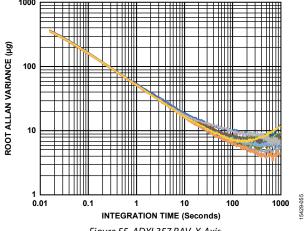

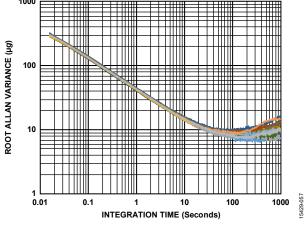

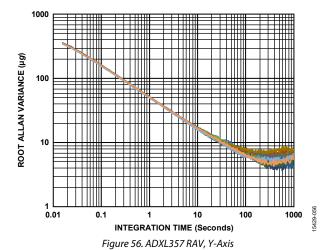

| Root Allan Variance (RAV) ADXL357 Characteristics 20               |

| Theory of Operation21                                              |

| Applications Information22                                         |

| Analog Output22                                                    |

| Digital Output22                                                   |

| Axes of Acceleration Sensitivity                                   |

| Power Sequencing                                                   |

| Power Supply Description                                           |

| Overrange Protection                                               |

| Self Test                                                          |

| Filter                                                             |

| Serial Communications26                                            |

| SPI Protocol                                                       |

| SPI Bus Sharing                                                    |

| I <sup>2</sup> C Protocol                                          |

| Reading Acceleration or Temperature Data from the Interface        |

| 27                                                                 |

| FIFO                                                               |

| Interrupts                                                         |

| DATA_RDY29                                                         |

| FIFO_FULL                                                      | 29 |

|----------------------------------------------------------------|----|

| FIFO_OVR                                                       | 29 |

| Activity                                                       | 29 |

| External Synchronization and Interpolation                     | 29 |

| ADXL357 Register Map                                           | 32 |

| Register Definitions                                           | 33 |

| Analog Devices ID Register                                     | 33 |

| Analog Devices MEMS ID Register                                | 33 |

| Device ID Register                                             | 33 |

| Product Revision ID Register                                   | 33 |

| Status Register                                                | 33 |

| FIFO Entries Register                                          | 34 |

| Temperature Data Registers                                     | 34 |

| X-Axis Data Registers                                          | 34 |

| Y-Axis Data Registers                                          | 35 |

| Z-Axis Data Registers                                          | 35 |

| FIFO Access Register                                           | 36 |

| X-Axis Offset Trim Registers                                   | 36 |

| Y-Axis Offset Trim Registers                                   | 36 |

| Z-Axis Offset Trim Registers                                   | 37 |

| Activity Enable Register                                       | 37 |

| Activity Threshold Registers                                   | 37 |

| Activity Count Register                                        | 37 |

| Filter Settings Register                                       | 38 |

| FIFO Samples Register                                          | 38 |

| Interrupt Pin (INTx) Function Map Register                     | 38 |

| Data Synchronization                                           | 39 |

| I <sup>2</sup> C Speed, Interrupt Polarity, and Range Register | 39 |

| Power Control Register                                         | 39 |

| Self Test Register                                             | 40 |

| Reset Register                                                 | 40 |

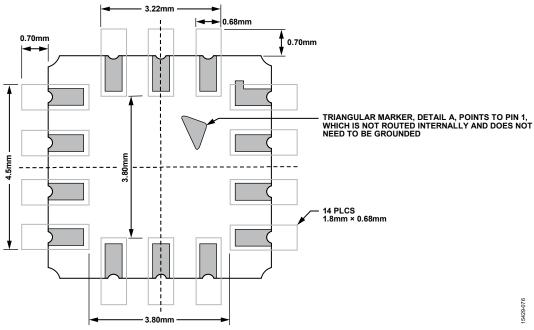

| PCB Footprint Pattern                                          | 41 |

| Outline Dimensions                                             | 42 |

| Ordering Guide                                                 | 12 |

#### **REVISION HISTORY**

| 6/2020—Rev. 0 to Rev. A                                               |

|-----------------------------------------------------------------------|

| Changes to Features Section, Applications Section, and General        |

| Description Section1                                                  |

| Changes to Table 14                                                   |

| Changes to Table 25                                                   |

| Changes to Input Current Parameter, Table 3                           |

| Changes to Acceleration (Any Axis, 0.1 ms) Parameter, Table 5;        |

| Thermal Resistance Section; and Table 69                              |

| Moved Recommended Soldering Profile Section, Figure 5, and            |

| Table 79                                                              |

| Changes to Table 810                                                  |

| Changes to Typical Performance Section and Figure 8 to                |

| Figure 13                                                             |

| Changes to Figure 14 to Figure 1913                                   |

| Changes to Figure 23 to Figure 2514                                   |

| Changes to Figure 32 to Figure 3716                                   |

| Changes to Figure 44 Caption, Figure 47 Caption, and Figure 48        |

| Caption                                                               |

| Changes to Figure 50 Caption, Figure 52 Caption, and                  |

| Figure 53                                                             |

| Changes to Theory of Operation Section21                              |

| Changes to Power Sequencing Section, V <sub>1P8ANA</sub> Section, and |

| Overrange Protection Section23                                        |

| Changes to Self Test Section, Filter Section, Figure 62, and          |

| Figure 63                                                             |

| Changes to Table 1125                                                 |

| Changes to Serial Communications Section and Figure $64 \ldots 26$    |

| Added SPI Bus Sharing Section and Figure 65; Renumbered               |

| Sequentially26                                                        |

| Changes to I <sup>2</sup> C Protocol Section27                        |

| Changes to FIFO Section                                               |

| Changes to DRDY Pin Section, FIFO_OVR Section, Activity       |

|---------------------------------------------------------------|

| Section, NVM_BUSY Section, and External Synchronization       |

| and Interpolation Section                                     |

| Changed EXT_SYNC = 00—No External Sync or Interpolation       |

| Section to EXT_SYNC = 00, EXT_CLK = 0—No External             |

| Synchronization or Interpolation Section; EXT_SYNC = 10—      |

| External Sync with Interpolation Section to EXT_SYNC = 10,    |

| EXT_CLK = 0—External Synchronization with Interpolation       |

| Section; and EXT_SYNC = 01—External Sync and External         |

| Clock, No Interpolation Filter Section to EXT_SYNC = 01,      |

| EXT_CLK = 1—External Synchronization and External Clock,      |

| No Interpolation Filter Section30                             |

| Changes to EXT_SYNC = 00, EXT_CLK = 0—No External             |

| Synchronization or Interpolation Section, EXT_SYNC = 10,      |

| EXT_CLK = 0—External Synchronization with Interpolation       |

| Section, Table 13, and EXT_SYNC = 01, EXT_CLK = 1—            |

| External Synchronization and External Clock, No Interpolation |

| Filter Section                                                |

| Added EXT_SYNC = 10, EXT_CLK = 1—External                     |

| Synchronization and External Clock, with Interpolation Filter |

| Section                                                       |

| Changes to Table 1431                                         |

| Changes to Figure 74, Figure 75 Caption, and Figure 7631      |

| Changes to Temperature Data Registers Section, Table 23,      |

| Table 24, and Table 2534                                      |

| Changes to Table 27, Table 28, Table 30 and Table 3135        |

| Change to Table 42 Title37                                    |

| Changes to Table 44                                           |

| Changes to Reset Register Section40                           |

| Changes to Figure 7741                                        |

| Changes to Ordering Guide42                                   |

2/2017—Revision 0: Initial Version

## **SPECIFICATIONS**

#### **ANALOG OUTPUT FOR THE ADXL356**

$T_A = 25$ °C,  $V_{SUPPLY} = 3.3$  V, x-axis acceleration and y-axis acceleration = 0 g, z-axis acceleration = 1 g, and full-scale range =  $\pm 10$  g, unless otherwise noted.

Table 1.

| Parameter                                                            | Test Conditions/Comments                                                      | Min                 | Тур      | Max   | Unit            |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------|----------|-------|-----------------|

| SENSOR INPUT                                                         | Each axis                                                                     |                     |          |       |                 |

| Output Full-Scale Range (FSR)                                        | ADXL356B supports two ranges                                                  |                     | ±10, ±20 |       | g               |

|                                                                      | ADXL356C supports two ranges                                                  |                     | ±10, ±40 |       | g               |

| Resonant Frequency <sup>1</sup>                                      |                                                                               |                     | 5.5      |       | kHz             |

| Nonlinearity                                                         | ±10 g                                                                         |                     | 0.1      |       | % FSR           |

|                                                                      | ±40 g                                                                         |                     | 1.3      |       | % FSR           |

| Cross Axis Sensitivity                                               |                                                                               |                     | 1        |       | %               |

| SENSITIVITY                                                          | Ratiometric to V <sub>1P8ANA</sub>                                            |                     |          |       |                 |

| Sensitivity at Xout, Yout, Zout                                      | ±10 g                                                                         | 73.6                | 80       | 86.4  | mV/ <i>g</i>    |

|                                                                      | ±20 g                                                                         | 36.8                | 40       | 43.2  | mV/ <i>g</i>    |

|                                                                      | ±40 g                                                                         | 18.4                | 20       | 21.6  | mV/ <i>g</i>    |

| Sensitivity Change Due to Temperature                                | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                          |                     | ±0.01    |       | %/°C            |

| Repeatability <sup>2</sup>                                           | X-axis and y-axis                                                             |                     | 0.1      |       | %               |

|                                                                      | Z-axis                                                                        |                     | 0.2      |       | %               |

| 0 g OFFSET                                                           | Each axis, ±10 g                                                              |                     |          |       |                 |

| 0 g Output for Хоит, Yоит, Zоит                                      | Referred to V <sub>1P8ANA</sub> /2                                            | -375                | ±125     | +375  | m <i>g</i>      |

| 0 g Offset vs. Temperature (X-Axis, Y-Axis, and Z-Axis) <sup>3</sup> | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                          | -0.75               | ±0.2     | +0.75 | m <i>g/</i> °C  |

| Repeatability <sup>2</sup>                                           | X-axis and y-axis                                                             |                     | ±4.25    |       | m <i>g</i>      |

|                                                                      | Z-axis                                                                        |                     | ±5       |       | m <i>g</i>      |

| Vibration Rectification Error (VRE) <sup>4</sup>                     | Offset due to 7.5 $g$ rms vibration, $\pm 10 g$ range, in a 1 $g$ orientation |                     | <0.1     |       | g               |

| NOISE                                                                |                                                                               |                     |          |       |                 |

| Spectral Density⁵                                                    |                                                                               |                     |          |       |                 |

| X-Axis, Y-Axis, and Z-Axis                                           | ±10 g                                                                         |                     | 75       |       | μ <i>g</i> /√Hz |

|                                                                      | ±40 g                                                                         |                     | 110      |       | μ <i>g</i> /√Hz |

| Velocity Random Walk                                                 | ±10 g                                                                         |                     |          |       |                 |

| X-Axis and Y-Axis                                                    |                                                                               |                     | 38.2     |       | mm/sec/√Hr      |

| Z-Axis                                                               |                                                                               |                     | 26.5     |       | mm/sec/√Hr      |

| BANDWIDTH                                                            | −3 dB, overall transfer function <sup>6</sup>                                 |                     | 2.4      |       | kHz             |

| SELF TEST                                                            | ·                                                                             |                     |          |       |                 |

| Output Change                                                        |                                                                               |                     |          |       |                 |

| Z-Axis                                                               | ±10 <i>g</i> range <sup>7</sup>                                               | 0.5                 | 1.25     | 3.0   | g               |

| POWER SUPPLY                                                         |                                                                               |                     |          |       |                 |

| Voltage Range                                                        |                                                                               |                     |          |       |                 |

| V <sub>SUPPLY</sub> <sup>8</sup>                                     |                                                                               | 2.25                | 2.5      | 3.6   | V               |

| V <sub>DDIO</sub>                                                    |                                                                               | V <sub>1P8DIG</sub> | 2.5      | 3.6   | V               |

| V <sub>1P8ANA</sub> , V <sub>1P8DIG</sub>                            | Internal low dropout (LDO) regulator bypassed, V <sub>SUPPLY</sub> = 0 V      | 1.62                | 1.8      | 1.98  | V               |

| Current                                                              |                                                                               |                     |          |       |                 |

| Measurement Mode                                                     |                                                                               |                     |          |       |                 |

| V <sub>SUPPLY</sub>                                                  | LDO regulator enabled                                                         |                     | 150      |       | μΑ              |

| V <sub>1P8ANA</sub>                                                  | LDO regulator disabled                                                        |                     | 138      |       | μΑ              |

| V <sub>1P8DIG</sub>                                                  | LDO regulator disabled                                                        |                     | 12       |       | μΑ              |

| Parameter                   | Test Conditions/Comments        | Min  | Тур | Max               | Unit  |

|-----------------------------|---------------------------------|------|-----|-------------------|-------|

| Standby Mode                |                                 |      |     |                   |       |

| $V_{\sf SUPPLY}$            | LDO regulator enabled           |      | 21  |                   | μΑ    |

| <b>V</b> 1P8ANA             | LDO regulator disabled          |      | 7   |                   | μΑ    |

| $V_{1P8DIG}$                | LDO regulator disabled          |      | 10  |                   | μΑ    |

| Turn On Time <sup>9</sup>   | 10 <i>g</i> range               |      | <10 |                   | ms    |

|                             | Power-off to standby            |      | <10 |                   | ms    |

| OUTPUT AMPLIFIER            | Хоит, Yоит, Zоит, and TEMP pins |      |     |                   |       |

| Swing                       | No load                         | 0.03 |     | $V_{1P8ANA}-0.03$ | V     |

| Output Series Resistance    |                                 |      | 32  |                   | kΩ    |

| TEMPERATURE SENSOR          |                                 |      |     |                   |       |

| Output at 25°C              |                                 |      | 967 |                   | mV    |

| Scale Factor                |                                 |      | 3.0 |                   | mV/°C |

| TEMPERATURE                 |                                 |      |     |                   |       |

| Operating Temperature Range |                                 | -40  |     | +125              | °C    |

<sup>&</sup>lt;sup>1</sup> The resonant frequency is a sensor characteristic.

$^3$  The temperature change is  $-40^{\circ}$ C to  $+25^{\circ}$ C, or  $+25^{\circ}$ C to  $+125^{\circ}$ C.

<sup>5</sup> Based on characterization.

<sup>7</sup> ±10 q indicates a test condition. The self test result converted to the acceleration value is independent of the selected range.

#### **DIGITAL OUTPUT FOR THE ADXL357**

$T_A = 25$ °C,  $V_{SUPPLY} = 3.3$  V, x-axis acceleration and y-axis acceleration = 0 g, z-axis acceleration = 1 g, full-scale range =  $\pm 10$  g, and output data rate (ODR) = 500 Hz, unless otherwise noted. Note that multifunction pin names may be referenced only by their relevant function.

Table 2.

| Parameter                                                                   | Test Conditions/Comments                             | Min    | Тур                 | Max    | Unit            |

|-----------------------------------------------------------------------------|------------------------------------------------------|--------|---------------------|--------|-----------------|

| SENSOR INPUT                                                                | Each axis                                            |        |                     |        |                 |

| Output Full Scale Range (FSR)                                               | User selectable, supports three ranges               |        | ±10,<br>±20,<br>±40 |        | g               |

| Nonlinearity                                                                | ±10 g                                                |        | 0.1                 |        | % FSR           |

|                                                                             | ±40 g                                                |        | 1.3                 |        | % FSR           |

| Cross Axis Sensitivity                                                      |                                                      |        | 1                   |        | %               |

| SENSITIVITY <sup>1</sup>                                                    | Each axis                                            |        |                     |        |                 |

| X-Axis, Y-Axis, and Z-Axis Sensitivity                                      | ±10 g                                                | 47,104 | 51,200              | 55,296 | LSB/g           |

|                                                                             | ±20 g                                                | 23,552 | 25,600              | 27,648 | LSB/g           |

|                                                                             | ±40 g                                                | 11,776 | 12,800              | 13,824 | LSB/g           |

| X-Axis, Y-Axis, and Z-Axis Scale Factor                                     | ±10 g                                                |        | 19.5                |        | μ <i>g/</i> LSB |

|                                                                             | ±20 g                                                |        | 39                  |        | μ <i>g/</i> LSB |

|                                                                             | ±40 g                                                |        | 78                  |        | μ <i>g/</i> LSB |

| Sensitivity Change due to Temperature                                       | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |        | ±0.01               |        | %/°C            |

| Repeatability <sup>2</sup>                                                  | X-axis and y-axis                                    |        | 0.1                 |        | %               |

|                                                                             | Z-axis                                               |        | 0.2                 |        | %               |

| 0 g OFFSET                                                                  | Each axis, ±10 g                                     |        |                     |        |                 |

| X-Axis, Y-Axis, and Z-Axis 0 g Output                                       |                                                      | -375   | ±125                | +375   | m <i>g</i>      |

| 0 <i>g</i> Offset vs. Temperature (X-Axis, Y-Axis, and Z-Axis) <sup>3</sup> | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | -0.75  | ±0.20               | +0.75  | m <i>g/</i> °C  |

<sup>&</sup>lt;sup>2</sup> Repeatability is predicted for a 10 year life and includes shifts due to the high temperature operating life (HTOL) ( $T_A = 150^{\circ}$ C,  $V_{SUPPLY} = 3.6$  V, and 1000 hours), temperature cycling (−55°C to +125°C and 1000 cycles), velocity random walk, broadband noise, and temperature hysteresis. Repeatability in relation to time follows the square root law. For example, to obtain offset repeatability of the x-axis for 2.5 years, use the following equation: ±4.25 mg × √(2.5 years/10 years) = ±2.125 mg.

<sup>&</sup>lt;sup>4</sup> The VRE measurement is the shift in dc offset while the device is subject to 7.5 g rms of random vibration from 50 Hz to 2 kHz. The device under test (DUT) is configured for the ±10 g range and an output data rate of 4 kHz. The VRE scales with the range setting.

$<sup>^{6}</sup>$  Overall transfer function includes the sensor mechanical response and all other filters on the signal chain.

<sup>8</sup> When VIPBANA and VIPBANA are generated internally, VSUPPLY is valid. To disable the LDO regulator and drive VIPBANA and VIPBANA and VORDIG externally, connect VSUPPLY to VSS.

$<sup>^{9}</sup>$  Standby to measurement mode. This specification is valid when the output is within  $^{5}$  mg of the final value.

| Parameter                                                                 | Test Conditions/Comments                                                      | Min                 | Тур   | Max  | Unit            |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------|-------|------|-----------------|

| Repeatability <sup>2</sup>                                                | X-axis and y-axis                                                             |                     | ±4.25 |      | m <i>g</i>      |

|                                                                           | Z-axis                                                                        |                     | ±5    |      | m <i>g</i>      |

| VRE <sup>4</sup>                                                          | Offset due to 7.5 $g$ rms vibration, $\pm 10 g$ range, in a 1 $g$ orientation |                     | <0.1  |      | g               |

| NOISE                                                                     |                                                                               |                     |       |      |                 |

| Spectral Density <sup>5</sup>                                             |                                                                               |                     |       |      |                 |

| X-Axis, Y-Axis, and Z-Axis                                                | ±10 g                                                                         |                     | 75    |      | μ <i>g</i> /√Hz |

|                                                                           | ±40 g                                                                         |                     | 90    |      | μ <i>g</i> /√Hz |

| Velocity Random Walk                                                      | ±10 g                                                                         |                     |       |      |                 |

| X-Axis and Y-Axis                                                         |                                                                               |                     | 38.2  |      | mm/sec/√H       |

| Z-Axis                                                                    |                                                                               |                     | 26.5  |      | mm/sec/√H       |

| BANDWIDTH AND OUTPUT DATA RATE                                            |                                                                               |                     |       |      |                 |

| Analog-to-Digital Converter (ADC) Resolution                              |                                                                               |                     | 20    |      | Bits            |

| Low-Pass Filter Passband Frequency                                        | User programmable, Register 0x28                                              | 0.977               |       | 1000 | Hz              |

| High-Pass Filter Passband Frequency When<br>Enabled (Disabled by Default) | User programmable, Register 0x28 for 4 kHz<br>ODR                             | 0.0095              |       | 10   | Hz              |

| SELF TEST                                                                 |                                                                               |                     |       |      |                 |

| Output Change                                                             |                                                                               |                     |       |      |                 |

| Z-Axis                                                                    | ±10 <i>q</i> range <sup>6</sup>                                               | 0.5                 | 1.25  | 3.0  | g               |

| POWER SUPPLY                                                              | ±10 g runge                                                                   | 0.5                 | 1.23  | 3.0  | 9               |

| Voltage Range                                                             |                                                                               |                     |       |      |                 |

| V <sub>SUPPLY</sub> Operating <sup>7</sup>                                |                                                                               | 2.25                | 2.5   | 3.6  | V               |

| Vodio                                                                     |                                                                               | V <sub>1P8DIG</sub> | 2.5   | 3.6  | V               |

| VIPRANA and VIPRDIG                                                       | Internal LDO regulator bypassed, V <sub>SUPPLY</sub> = 0 V                    | 1.62                | 1.8   | 1.98 | V               |

| Current                                                                   | internal EDG regulator Sypussea, V30FFEI                                      | 1.02                | 1.0   | 1.50 |                 |

| Measurement Mode                                                          |                                                                               |                     |       |      |                 |

| Vsupply                                                                   | LDO regulator enabled                                                         |                     | 200   |      | μA              |

| V <sub>1P8ANA</sub>                                                       | LDO regulator disabled                                                        |                     | 160   |      | μΑ              |

| V <sub>1P8DIG</sub>                                                       | LDO regulator disabled                                                        |                     | 35.5  |      | μA              |

| Standby Mode                                                              |                                                                               |                     | 55.5  |      | F               |

| Vsupply                                                                   | LDO regulator enabled                                                         |                     | 21    |      | μA              |

| V <sub>1P8ANA</sub>                                                       | LDO regulator disabled                                                        |                     | 7     |      | μΑ              |

| V <sub>1P8DIG</sub>                                                       | LDO regulator disabled                                                        |                     | 10    |      | μΑ              |

| Turn On Time <sup>8</sup>                                                 | ±10 g range                                                                   |                     | <10   |      | ms              |

|                                                                           | Power-off to standby                                                          |                     | <10   |      | ms              |

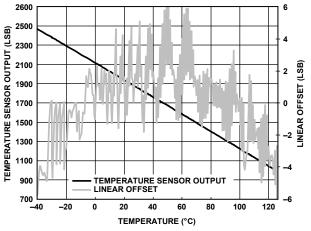

| TEMPERATURE SENSOR                                                        | ,                                                                             | 1                   | -     |      |                 |

| Output at 25°C                                                            |                                                                               |                     | 1885  |      | LSB             |

| Scale Factor                                                              |                                                                               |                     | -9.05 |      | LSB/°C          |

| TEMPERATURE                                                               |                                                                               | 1                   |       |      |                 |

| Operating Temperature Range                                               |                                                                               | -40                 |       | +125 | °C              |

<sup>&</sup>lt;sup>1</sup> Characterized but not 100% tested.

<sup>&</sup>lt;sup>2</sup> Repeatability is predicted for a 10 year life and includes shifts due to the HTOL ( $T_A = 150^{\circ}\text{C}$ ,  $V_{\text{SUPPLY}} = 3.6 \text{ V}$ , and 1000 hours), temperature cycling ( $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and 1000 cycles), velocity random walk, broadband noise, and temperature hysteresis. Repeatability in relation to time follows the square root law. For example, to obtain offset repeatability of the x-axis for 2.5 years, use the following equation:  $\pm 4.25 \text{ mg} \times \sqrt{(2.5 \text{ years/10 years})} = \pm 2.125 \text{ mg}$ .

$<sup>^3</sup>$  The temperature change is  $-40^{\circ}$ C to  $+25^{\circ}$ C or  $+25^{\circ}$ C to  $+125^{\circ}$ C.

<sup>&</sup>lt;sup>4</sup> The VRE measurement is the shift in dc offset while the device is subject to 7.5 g rms random vibration from 50 Hz to 2 kHz. The DUT is configured for the ±10 g range and an output data rate of 4 kHz. The VRE scales with the range setting.

<sup>&</sup>lt;sup>5</sup> Based on characterization.

$<sup>^6</sup>$  ±10 g indicates a test condition. The self test result converted to the acceleration value is independent of the selected range.

$<sup>^{7}</sup>$  When  $V_{1P8ANA}$  and  $V_{1P8DIG}$  are generated internally,  $V_{SUPPLY}$  is valid. To disable the LDO regulator and drive  $V_{1P8ANA}$  and  $V_{1P8DIG}$  externally, connect  $V_{SUPPLY}$  to  $V_{SS}$ .

<sup>&</sup>lt;sup>8</sup> Standby to measurement mode. This specification is valid when the output is within 1 mq of final value.

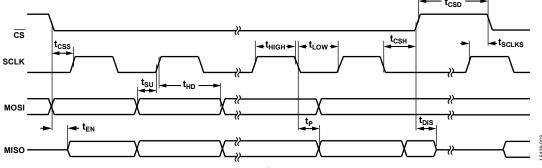

#### SPI DIGITAL INTERFACE CHARACTERISTICS FOR THE ADXL357

Note that multifunction pin names may be referenced by their relevant function only.

Table 3.

| Parameter              | Symbol                  | Test Conditions/Comments                      | Min                   | Тур | Max                          | Unit |

|------------------------|-------------------------|-----------------------------------------------|-----------------------|-----|------------------------------|------|

| DC INPUT LEVELS        |                         |                                               |                       |     |                              |      |

| Input Voltage          |                         |                                               |                       |     |                              |      |

| Low Level              | VIL                     |                                               |                       |     | $0.3 \times V_{DDIO}$        | V    |

| High Level             | V <sub>IH</sub>         |                                               | $0.7 \times V_{DDIO}$ |     |                              | V    |

| Input Current          |                         |                                               |                       |     |                              |      |

| Low Level              | I₁∟                     | Input voltage $(V_{IN}) = 0 V$                | -0.2                  |     |                              | μΑ   |

| High Level             | I <sub>IH</sub>         | $V_{IN} = V_{DDIO}$                           |                       |     | 0.2                          | μΑ   |

| DC OUTPUT LEVELS       |                         |                                               |                       |     |                              |      |

| Output Voltage         |                         |                                               |                       |     |                              |      |

| Low Level              | VoL                     | I <sub>OL</sub> = I <sub>OL</sub> , MIN       |                       |     | $0.2 \times V_{\text{DDIO}}$ | V    |

| High Level             | V <sub>OH</sub>         | $I_{OH} = I_{OH, MAX}$                        | $0.8 \times V_{DDIO}$ |     |                              | V    |

| Output Current         |                         |                                               |                       |     |                              |      |

| Low Level              | I <sub>OL</sub>         | $V_{OL} = V_{OL, MAX}$                        | -10                   |     |                              | mA   |

| High Level             | Іон                     | $V_{OH} = V_{OH, MIN}$                        |                       |     | 4                            | mA   |

| AC INPUT LEVELS        |                         |                                               |                       |     |                              |      |

| SCLK Frequency         |                         |                                               | 0.1                   |     | 10                           | MHz  |

| SCLK High Time         | t <sub>HIGH</sub>       |                                               | 40                    |     |                              | ns   |

| SCLK Low Time          | t <sub>LOW</sub>        |                                               | 40                    |     |                              | ns   |

| CS Setup Time          | t <sub>CSS</sub>        |                                               | 20                    |     |                              | ns   |

| CS Hold Time           | <b>t</b> <sub>CSH</sub> |                                               | 20                    |     |                              | ns   |

| CS Disable Time        | t <sub>CSD</sub>        |                                               | 40                    |     |                              | ns   |

| Rising SCLK Setup Time | t <sub>SCLKS</sub>      |                                               | 20                    |     |                              | ns   |

| MOSI Setup Time        | t <sub>SU</sub>         |                                               | 20                    |     |                              | ns   |

| MOSI Hold Time         | t <sub>HD</sub>         |                                               | 20                    |     |                              | ns   |

| AC OUTPUT LEVELS       |                         |                                               |                       |     |                              |      |

| Propagation Delay      | t₽                      | Load capacitance $(C_{LOAD}) = 30 \text{ pF}$ |                       |     | 30                           | ns   |

| Enable MISO Time       | t <sub>EN</sub>         |                                               | 30                    |     |                              | ns   |

| Disable MISO Time      | t <sub>DIS</sub>        |                                               |                       |     | 20                           | ns   |

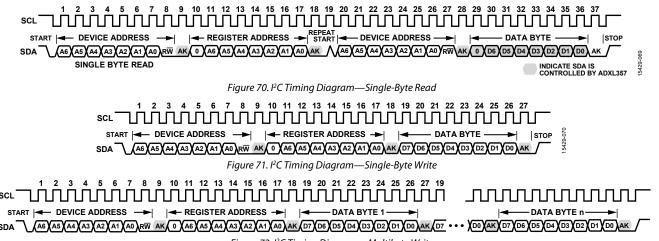

Figure 3. SPI Interface Timing Diagram

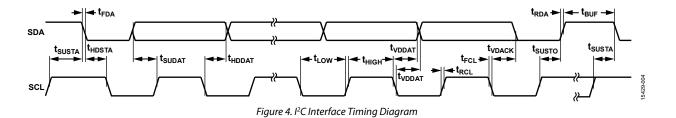

#### I<sup>2</sup>C DIGITAL INTERFACE CHARACTERISTICS FOR THE ADXL357

Note that multifunction pin names may be referenced only by their relevant function.

Table 4.

|                                           | 1                  | Test Conditions/                                                                         | I2C_HS = 0 (Fast Mode)           |     | 12C_HS = 1            | (High S               | peed Mode) |                       |      |

|-------------------------------------------|--------------------|------------------------------------------------------------------------------------------|----------------------------------|-----|-----------------------|-----------------------|------------|-----------------------|------|

| Parameter                                 | Symbol             | Comments                                                                                 | Min                              | Тур | Max                   | Min                   | Тур        | Max                   | Unit |

| DC INPUT LEVELS                           |                    |                                                                                          |                                  |     |                       |                       |            |                       |      |

| Input Voltage                             |                    |                                                                                          |                                  |     |                       |                       |            |                       |      |

| Low Level                                 | V <sub>IL</sub>    |                                                                                          |                                  |     | $0.3 \times V_{DDIO}$ |                       |            | $0.3 \times V_{DDIO}$ | V    |

| High Level                                | V <sub>IH</sub>    |                                                                                          | $0.7 \times V_{DDIO}$            |     |                       | $0.7 \times V_{DDIO}$ |            |                       | V    |

| Hysteresis of Schmitt<br>Triggered Inputs | V <sub>HYS</sub>   |                                                                                          | $0.05 \times V_{DDIO}$           |     |                       | $0.1 \times V_{DDIO}$ |            |                       | V    |

| Input Current                             | I <sub>IL</sub>    | $ \begin{array}{c c} 0.1 \times V_{DDIO} < V_{IN} < \\ 0.9 \times V_{DDIO} \end{array} $ | -10                              |     | +10                   |                       |            |                       | μΑ   |

| DC OUTPUT LEVELS                          |                    |                                                                                          |                                  |     |                       |                       |            |                       |      |

| Output Voltage                            |                    | $I_{OL} = 3 \text{ mA}$                                                                  |                                  |     |                       |                       |            |                       |      |

| Low Level                                 | $V_{OL1}$          | $V_{DDIO} > 2 V$                                                                         |                                  |     | 0.4                   |                       |            | 0.4                   | V    |

|                                           | V <sub>OL2</sub>   | $V_{DDIO} \leq 2 V$                                                                      |                                  |     | $0.2 \times V_{DDIO}$ |                       |            | $0.2 \times V_{DDIO}$ | V    |

| Output Current                            |                    |                                                                                          |                                  |     |                       |                       |            |                       |      |

| Low Level                                 | I <sub>OL</sub>    | $V_{OL} = 0.4 V$                                                                         | 20                               |     |                       | 20                    |            |                       | mA   |

|                                           |                    | $V_{OL} = 0.6 \text{ V}$                                                                 | 6                                |     |                       | 6                     |            |                       | mA   |

| AC INPUT LEVELS                           |                    |                                                                                          |                                  |     |                       |                       |            |                       |      |

| SCL Frequency                             |                    |                                                                                          | 0                                |     | 1                     | 0                     |            | 3.4                   | MHz  |

| SCL High Time                             | t <sub>HIGH</sub>  |                                                                                          | 260                              |     |                       | 60                    |            |                       | ns   |

| SCL Low Time                              | t <sub>LOW</sub>   |                                                                                          | 500                              |     |                       | 160                   |            |                       | ns   |

| Start Setup Time                          | t <sub>SUSTA</sub> |                                                                                          | 260                              |     |                       | 160                   |            |                       | ns   |

| Start Hold Time                           | t <sub>HDSTA</sub> |                                                                                          | 260                              |     |                       | 160                   |            |                       | ns   |

| SDA Setup Time                            | tsudat             |                                                                                          | 50                               |     |                       | 10                    |            |                       | ns   |

| SDA Hold Time                             | t <sub>HDDAT</sub> |                                                                                          | 0                                |     |                       | 0                     |            |                       | ns   |

| Stop Setup Time                           | tsusto             |                                                                                          | 260                              |     |                       | 160                   |            |                       | ns   |

| Bus Free Time                             | t <sub>BUF</sub>   |                                                                                          | 500                              |     |                       |                       |            |                       | ns   |

| SCL Input Rise Time                       | t <sub>RCL</sub>   |                                                                                          |                                  |     | 120                   |                       |            | 80                    | ns   |

| SCL Input Fall Time                       | t <sub>FCL</sub>   |                                                                                          |                                  |     | 120                   |                       |            | 80                    | ns   |

| SDA Input Rise Time                       | t <sub>RDA</sub>   |                                                                                          |                                  |     | 120                   |                       |            | 160                   | ns   |

| SDA Input Fall Time                       | t <sub>FDA</sub>   |                                                                                          |                                  |     | 120                   |                       |            | 160                   | ns   |

| Width of Spikes to<br>Suppress            | t <sub>SP</sub>    | Not shown in Figure 4                                                                    |                                  |     | 50                    |                       |            | 10                    | ns   |

| AC OUTPUT LEVELS                          |                    |                                                                                          |                                  |     |                       |                       |            |                       |      |

| <b>Propagation Delay</b>                  |                    | $C_{LOAD} = 500 \text{ pF}$                                                              |                                  |     |                       |                       |            |                       |      |

| Data                                      | t <sub>VDDAT</sub> |                                                                                          | 97                               |     | 450                   | 27                    |            | 135                   | ns   |

| Acknowledge                               | t <sub>VDACK</sub> |                                                                                          |                                  |     | 450                   |                       |            |                       | ns   |

| Output Fall Time                          | t <sub>F</sub>     | Not shown in Figure 4                                                                    | 20 ×<br>(V <sub>DDIO</sub> /5.5) |     | 120                   |                       |            |                       | ns   |

#### **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| 1 0010 01                                                                      |                                              |

|--------------------------------------------------------------------------------|----------------------------------------------|

| Parameter                                                                      | Rating                                       |

| Acceleration (Any Axis, 0.1 ms)                                                |                                              |

| Unpowered                                                                      | 10,000 <i>g</i>                              |

| Powered                                                                        | 10,000 <i>g</i>                              |

| $V_{\text{SUPPLY}}$ , $V_{\text{DDIO}}$                                        | 5.4 V                                        |

| V <sub>1P8ANA</sub> , V <sub>1P8DIG</sub> Configured as Inputs                 | 1.98 V                                       |

| ADXL356                                                                        |                                              |

| Digital Inputs (RANGE, ST1, ST2, STBY)                                         | $-0.3 \text{ V to V}_{DDIO} + 0.3 \text{ V}$ |

| Analog Outputs (X <sub>OUT</sub> , Y <sub>OUT</sub> , Z <sub>OUT</sub> , TEMP) | -0.3 V to V <sub>1P8ANA</sub> + 0.3 V        |

| ADXL357                                                                        |                                              |

| Digital Pins (CS/SCL, SCLK/V <sub>SSIO</sub> ,                                 | $-0.3 \text{ V to V}_{DDIO} + 0.3 \text{ V}$ |

| MOSI/SDA, MISO/ASEL, INT1, INT2,                                               |                                              |

| DRDY)                                                                          |                                              |

| Operating Temperature Range                                                    | −40°C to +125°C                              |

| Storage Temperature Range                                                      | −55°C to +150°C                              |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\psi_{JB}$  is the junction to board thermal resistance.

**Table 6. Thermal Resistance**

| Package Type        | <b>Ө</b> ЈА | ψյв  | Unit |

|---------------------|-------------|------|------|

| E-14-1 <sup>1</sup> | 42          | 17.6 | °C/W |

<sup>&</sup>lt;sup>1</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board with four thermal vias. See JEDEC JESD51.

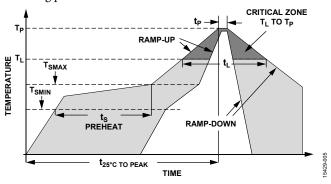

#### RECOMMENDED SOLDERING PROFILE

Figure 5 and Table 7 provide details about the recommended soldering profile.

Figure 5. Recommended Soldering Profile

**Table 7. Recommended Soldering Profile**

| Condition                                                                      |                      |                      |  |  |  |  |  |

|--------------------------------------------------------------------------------|----------------------|----------------------|--|--|--|--|--|

|                                                                                | Con                  | aition               |  |  |  |  |  |

| Profile Feature                                                                | Sn63/Pb37            | Pb-Free              |  |  |  |  |  |

| Average Ramp Rate from Liquid                                                  | 3°C/sec              | 3°C/sec              |  |  |  |  |  |

| Temperature (T <sub>L</sub> ) to Peak<br>Temperature (T <sub>P</sub> )         | maximum              | maximum              |  |  |  |  |  |

| Preheat                                                                        |                      |                      |  |  |  |  |  |

| Minimum Temperature<br>(T <sub>SMIN</sub> )                                    | 100°C                | 150°C                |  |  |  |  |  |

| $\begin{array}{c} \text{Maximum Temperature} \\ (T_{\text{SMAX}}) \end{array}$ | 150°C                | 200°C                |  |  |  |  |  |

| Time from T <sub>SMIN</sub> to T <sub>SMAX</sub> (ts)                          | 60 sec to            | 60 sec to            |  |  |  |  |  |

|                                                                                | 120 sec              | 180 sec              |  |  |  |  |  |

| $T_{SMAX}$ to $T_L$ Ramp-Up Rate                                               | 3°C/sec              | 3°C/sec              |  |  |  |  |  |

|                                                                                | maximum              | maximum              |  |  |  |  |  |

| Liquid Temperature (T <sub>L</sub> )                                           | 183°C                | 217°C                |  |  |  |  |  |

| Time Maintained Above $T_L$ ( $t_L$ )                                          | 60 sec to<br>150 sec | 60 sec to<br>150 sec |  |  |  |  |  |

| Peak Temperature (T <sub>P</sub> )                                             | 240°C +              | 260°C +              |  |  |  |  |  |

|                                                                                | 0°C/-5°C             | 0°C/-5°C             |  |  |  |  |  |

| Time of Actual $T_P - 5^{\circ}C$ ( $t_P$ )                                    | 10 sec to            | 20 sec to            |  |  |  |  |  |

|                                                                                | 30 sec               | 40 sec               |  |  |  |  |  |

| Ramp-Down Rate                                                                 | 6°C/sec              | 6°C/sec              |  |  |  |  |  |

|                                                                                | maximum              | maximum              |  |  |  |  |  |

| Time from 25°C to Peak                                                         | 6 minutes            | 8 minutes            |  |  |  |  |  |

| Temperature (t <sub>25°C TO PEAK</sub> )                                       | maximum              | maximum              |  |  |  |  |  |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

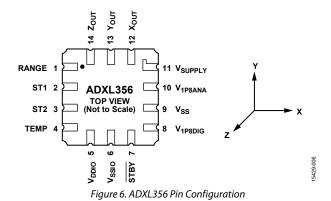

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

**Table 8. ADXL356 Pin Function Descriptions**

| Pin No. | Mnemonic            | Description                                                                                                                                                                                                                               |

|---------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | RANGE               | Range Selection Pin. Set this pin to ground to select the $\pm 10g$ range, or set this pin to $V_{DDIO}$ to select the $\pm 20g$ or $\pm 40g$ range. This pin is model dependent (see the Ordering Guide section).                        |

| 2       | ST1                 | Self Test Pin 1. This pin enables self test mode. This pin must be forced low when not in self test mode.                                                                                                                                 |

| 3       | ST2                 | Self Test Pin 2. This pin activates electromechanical self test actuation. This pin must be forced low when not in self test mode.                                                                                                        |

| 4       | TEMP                | Temperature Sensor Output.                                                                                                                                                                                                                |

| 5       | $V_{\text{DDIO}}$   | Digital Interface Supply Voltage.                                                                                                                                                                                                         |

| 6       | V <sub>SSIO</sub>   | Digital Ground.                                                                                                                                                                                                                           |

| 7       | STBY                | Standby or Measurement Mode Selection Pin. Set this pin to ground to enter standby mode, or set this pin to $V_{DDIO}$ to enter measurement mode.                                                                                         |

| 8       | V <sub>1P8DIG</sub> | Digital Supply. This pin requires a decoupling capacitor. If V <sub>SUPPLY</sub> connects to V <sub>SS</sub> , supply the voltage to this pin externally.                                                                                 |

| 9       | V <sub>SS</sub>     | Analog Ground.                                                                                                                                                                                                                            |

| 10      | V <sub>1P8ANA</sub> | Analog Supply. This pin requires a decoupling capacitor. If V <sub>SUPPLY</sub> connects to V <sub>SS</sub> , supply the voltage to this pin externally.                                                                                  |

| 11      | VSUPPLY             | Supply Voltage. When $V_{SUPPLY}$ equals 2.25 V to 3.6 V, $V_{SUPPLY}$ enables the internal LDO regulators to generate $V_{1PBDIG}$ and $V_{1PBANA}$ . For $V_{SUPPLY} = V_{SS}$ , $V_{1PBDIG}$ and $V_{1PBANA}$ are externally supplied. |

| 12      | X <sub>OUT</sub>    | X-Axis Output.                                                                                                                                                                                                                            |

| 13      | Yout                | Y-Axis Output.                                                                                                                                                                                                                            |

| 14      | Z <sub>OUT</sub>    | Z-Axis Output.                                                                                                                                                                                                                            |

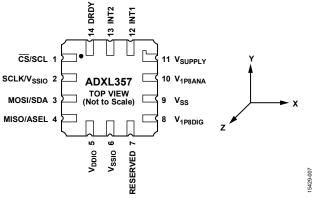

Figure 7. ADXL357 Pin Configuration (SPI/I<sup>2</sup>C)

**Table 9. ADXL357 Pin Function Descriptions**

| Pin No. | Mnemonic               | Description                                                                                                                                                                                                                                                                                         |

|---------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CS/SCL                 | Chip Select for SPI (CS).                                                                                                                                                                                                                                                                           |

|         |                        | Serial Communications Clock for I <sup>2</sup> C (SCL).                                                                                                                                                                                                                                             |

| 2       | SCLK/V <sub>SSIO</sub> | Serial Communications Clock for SPI (SCLK).                                                                                                                                                                                                                                                         |

|         |                        | I <sup>2</sup> C Mode Enable (V <sub>SSIO</sub> ). Connect this pin to Pin 6 (V <sub>SSIO</sub> ) to enable I <sup>2</sup> C mode.                                                                                                                                                                  |

| 3       | MOSI/SDA               | Master Output, Slave Input for SPI (MOSI).                                                                                                                                                                                                                                                          |

|         |                        | Serial Data for I <sup>2</sup> C (SDA).                                                                                                                                                                                                                                                             |

| 4       | MISO/ASEL              | Master Input, Slave Output for SPI (MISO).                                                                                                                                                                                                                                                          |

|         |                        | Alternate I <sup>2</sup> C Address Select for I <sup>2</sup> C (ASEL).                                                                                                                                                                                                                              |

| 5       | $V_{\text{DDIO}}$      | Digital Interface Supply Voltage.                                                                                                                                                                                                                                                                   |

| 6       | $V_{SSIO}$             | Digital Ground.                                                                                                                                                                                                                                                                                     |

| 7       | RESERVED               | Reserved. This pin can be connected to ground or left open.                                                                                                                                                                                                                                         |

| 8       | V <sub>1P8DIG</sub>    | Digital Supply. This pin requires a decoupling capacitor. If V <sub>SUPPLY</sub> connects to V <sub>SS</sub> , supply the voltage to this pin externally.                                                                                                                                           |

| 9       | V <sub>SS</sub>        | Analog Ground.                                                                                                                                                                                                                                                                                      |

| 10      | V <sub>1P8ANA</sub>    | Analog Supply. This pin requires a decoupling capacitor. If V <sub>SUPPLY</sub> connects to V <sub>SS</sub> , supply the voltage to this pin externally.                                                                                                                                            |

| 11      | VSUPPLY                | Supply Voltage. When V <sub>SUPPLY</sub> equals 2.25 V to 3.6 V, V <sub>SUPPLY</sub> enables the internal LDO regulators to generate V <sub>1P8DIG</sub> and V <sub>1P8ANA</sub> . For V <sub>SUPPLY</sub> = V <sub>SS</sub> , V <sub>1P8DIG</sub> and V <sub>1P8ANA</sub> are externally supplied. |

| 12      | INT1                   | Interrupt Pin 1.                                                                                                                                                                                                                                                                                    |

| 13      | INT2                   | Interrupt Pin 2.                                                                                                                                                                                                                                                                                    |

| 14      | DRDY                   | Data Ready Pin.                                                                                                                                                                                                                                                                                     |

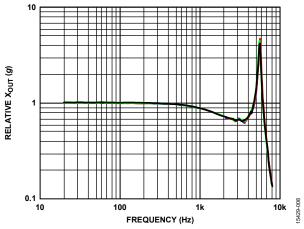

#### TYPICAL PERFORMANCE CHARACTERISTICS

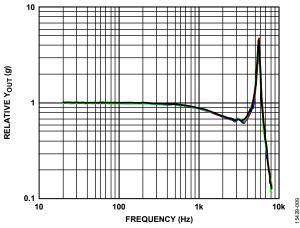

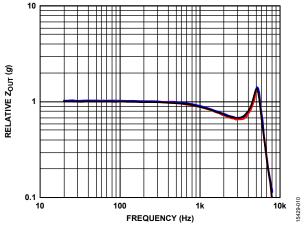

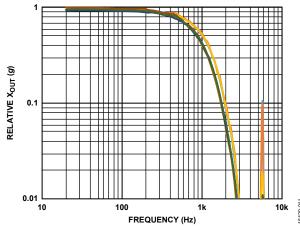

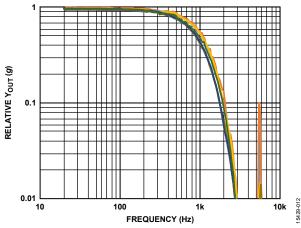

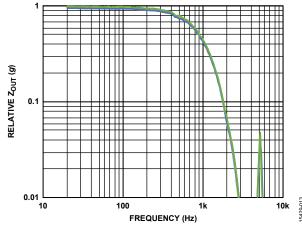

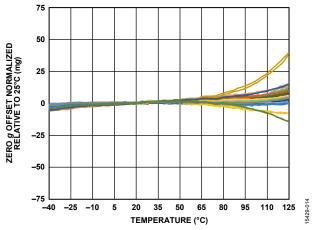

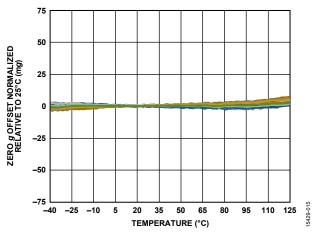

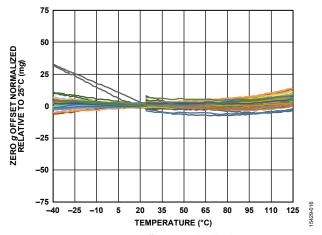

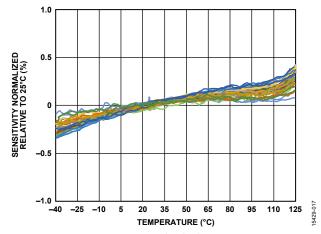

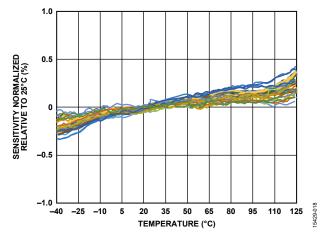

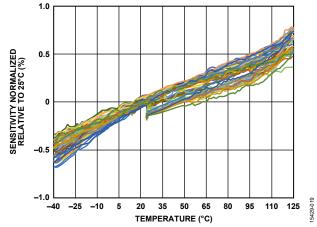

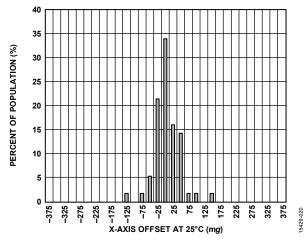

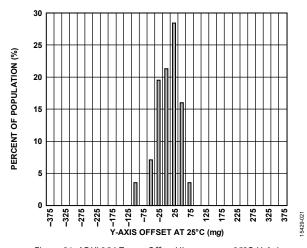

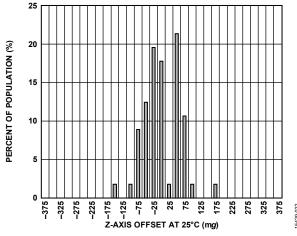

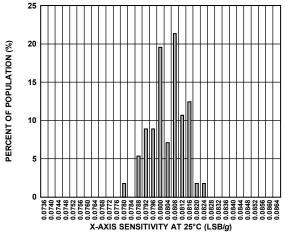

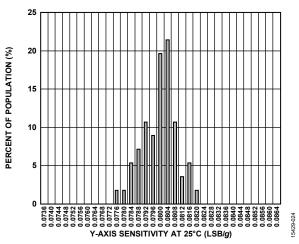

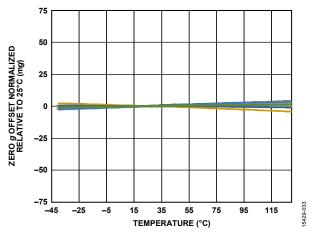

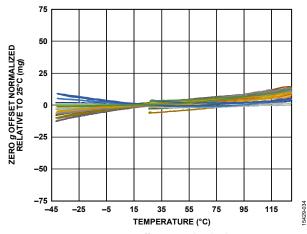

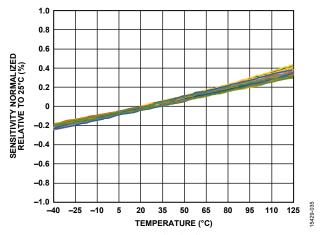

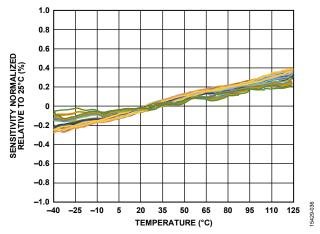

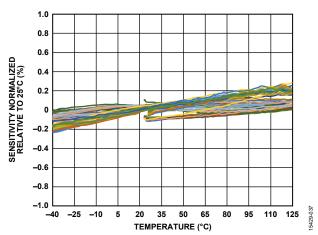

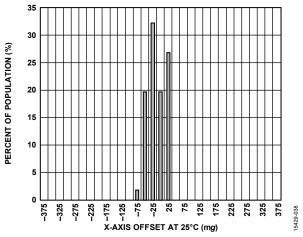

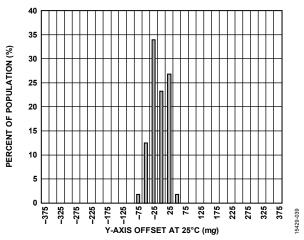

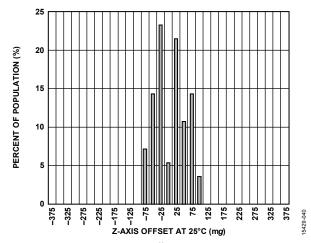

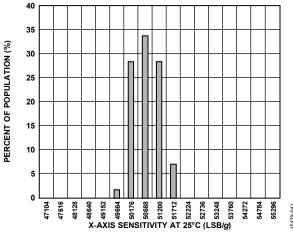

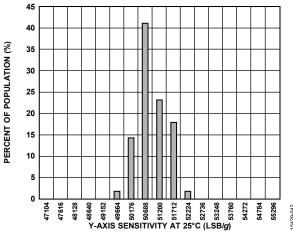

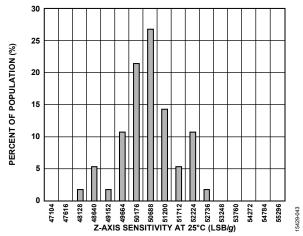

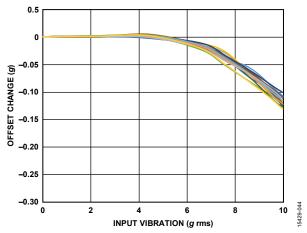

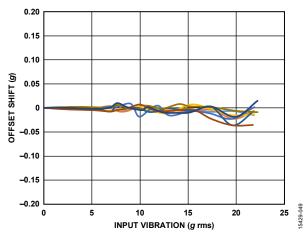

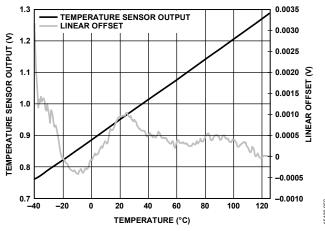

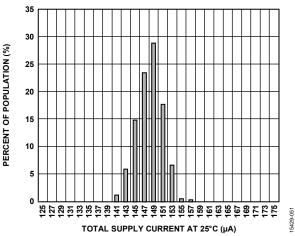

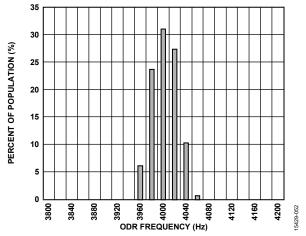

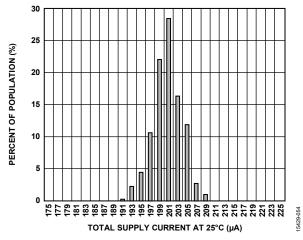

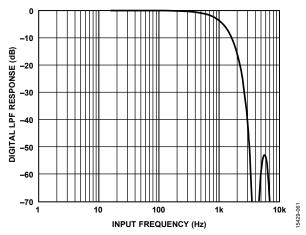

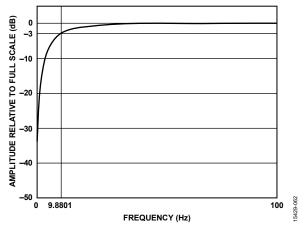

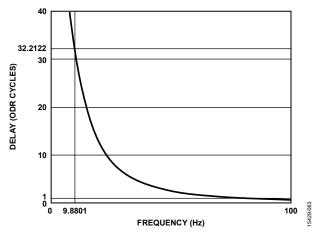

All figures include data for multiple devices and multiple lots, and they were taken in the  $\pm 10~g$  range and  $T_A = 25$ °C, unless otherwise noted. For Figure 52, the ODR is derived from a master clock, with a frequency of 1.024 MHz and  $\pm 1.4\%$  device to device variation (similar to ODR device to device variation). For a given device, however, clock frequency variation over the temperature range (-40°C to +125°C) is no more than  $\pm 1.2\%$ , guaranteed by design.

Figure 8. ADXL356 Frequency Response for X-Axis

Figure 9. ADXL356 Frequency Response for Y-Axis

Figure 10. ADXL356 Frequency Response for Z-Axis

Figure 11. ADXL357 Frequency Response for X-Axis at 4 kHz ODR

Figure 12. ADXL357 Frequency Response for Y-Axis at 4 kHz ODR

Figure 13. ADXL357 Frequency Response for Z-Axis at 4 kHz ODR

Figure 14. ADXL356 Zero g Offset Normalized Relative to 25°C vs. Temperature, X-Axis

Figure 15. ADXL356 Zero g Offset Normalized Relative to 25°C vs. Temperature, Y-Axis

Figure 16. ADXL356 Zero g Offset Normalized Relative to 25°C vs. Temperature, Z-Axis

Figure 17. ADXL356 Sensitivity Normalized Relative to 25  $^{\circ}$ C vs. Temperature X-Axis

Figure 18. ADXL356 Sensitivity Normalized Relative to 25  $^{\circ}$ C vs. Temperature, Y-Axis

Figure 19. ADXL356 Sensitivity Normalized Relative to 25°C vs. Temperature,

Figure 20. ADXL356 Zero g Offset Histogram at 25°C, X-Axis

Figure 21. ADXL356 Zero g Offset Histogram at 25°C, Y-Axis

Figure 22. ADXL356 Zero g Offset Histogram at 25°C, Z-Axis

Figure 23. ADXL356 Sensitivity Histogram at 25°C, X-Axis

Figure 24. ADXL356 Sensitivity Histogram at 25°C, Y-Axis

Figure 25. ADXL356 Sensitivity Histogram at 25°C, Z-Axis

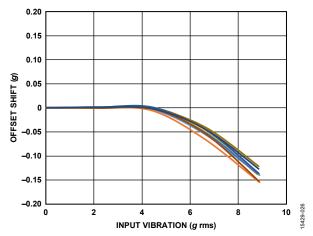

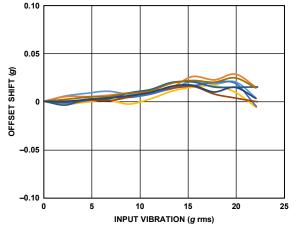

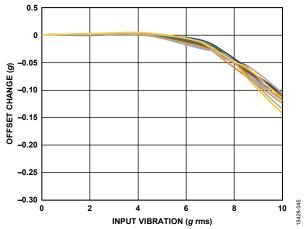

Figure 26. ADXL356 VRE, X-Axis Offset from +1 g,  $\pm 10$  g Range, X-Axis Orientation = +1 g

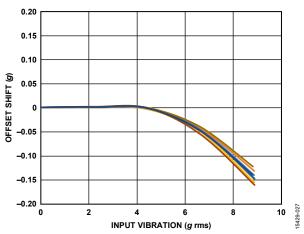

Figure 27. ADXL356 VRE, Y-Axis Offset from +1 g,  $\pm$ 10 g Range, Y-Axis Orientation = +1 g

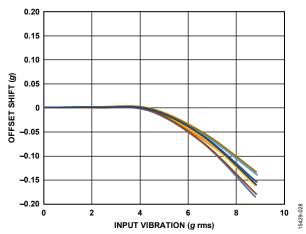

Figure 28. ADXL356 VRE, Z-Axis Offset from +1 g,  $\pm$ 10 g Range, Z-Axis Orientation = +1 g

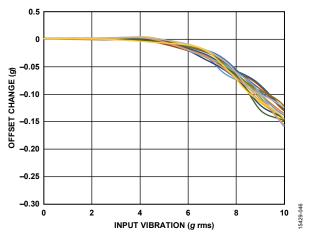

Figure 29. ADXL356 VRE, X-Axis Offset from -1 g,  $\pm 40$  g Range, X-Axis Orientation = -1 g

Figure 30. ADXL356 VRE, Y-Axis Offset from -1 g,  $\pm 40$  g Range, Y-Axis Orientation = -1 g

Figure 31. ADXL356 VRE, Z-Axis Offset from -1 g,  $\pm 40$  g Range, Z-Axis Orientation = -1 g

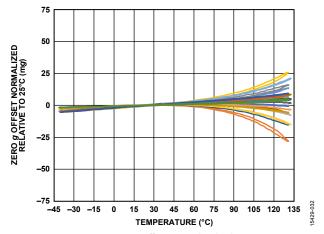

Figure 32. ADXL357 Zero g Offset Normalized Relative to 25°C vs. Temperature, X-Axis

Figure 33. ADXL357 Zero g Offset Normalized Relative to 25°C vs. Temperature, Y-Axis

Figure 34. ADXL357 Zero g Offset Normalized Relative to 25°C vs. Temperature, Z-Axis

Figure 35. ADXL357 Sensitivity Normalized Relative to 25°C vs. Temperature X-Axis

Figure 36. ADXL357 Sensitivity Normalized Relative to  $25^{\circ}$ C vs. Temperature Y-Axis

Figure 37. ADXL357 Sensitivity Normalized Relative to 25°C vs. Temperature

Figure 38. ADXL357 Zero g Offset Histogram at 25°C, X-Axis

Figure 39. ADXL357 Zero g Offset Histogram at 25°C, Y-Axis

Figure 40. ADXL357 Zero g Offset Histogram at 25 °C, Z-Axis

Figure 41. ADXL357 Sensitivity Histogram at 25°C, X-Axis

Figure 42. ADXL357 Sensitivity Histogram at 25°C, Y-Axis

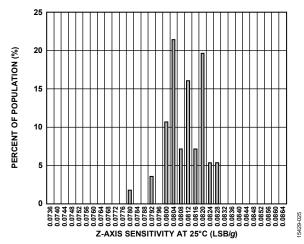

Figure 43. ADXL357 Sensitivity Histogram at 25°C, Z-Axis

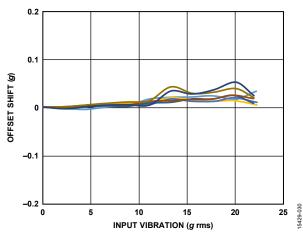

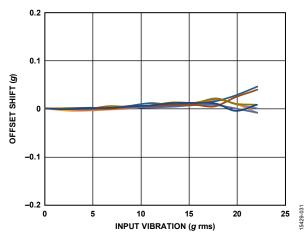

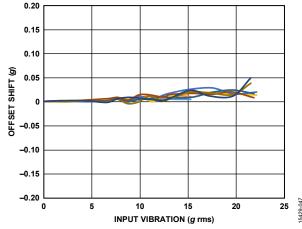

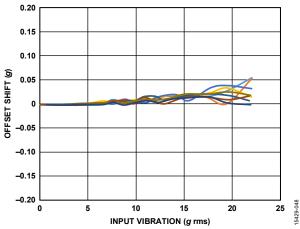

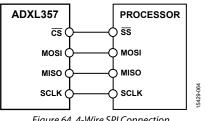

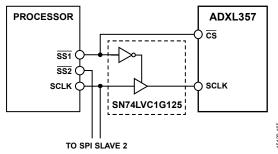

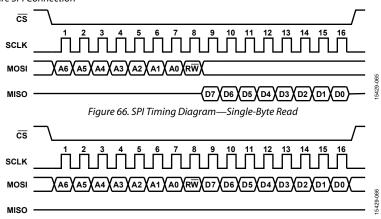

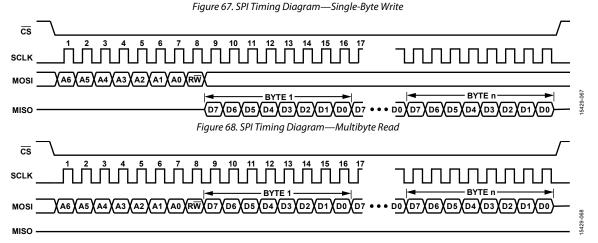

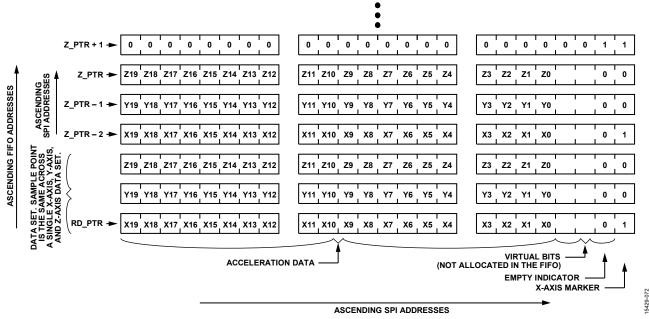

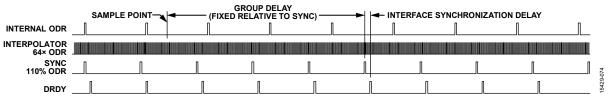

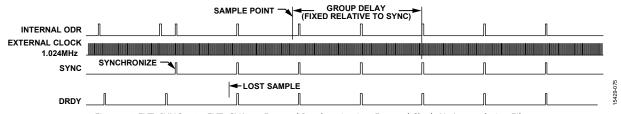

Figure 44. ADXL357 VRE, X-Axis Offset from +1 g,  $\pm 10$  g Range, X-Axis Orientation = +1 g